# LF to 4 GHz High Linearity Y-Mixer

**Preliminary Technical Data**

ADL5350

#### **FEATURES**

Broadband radio frequency (RF), intermediate frequency (IF), and local oscillator (LO) ports

Conversion loss: 6.8 dB Noise figure: 6.5 dB High input IP3: 25 dBm High input P1dB: 19 dBm Low LO drive level

Single-ended design: no need for baluns Single-supply operation: 3 V @ 19 mA Miniature 8-lead 3 mm x 2 mm LFCSP

**RoHS compliant**

#### **APPLICATIONS**

Cellular base station

Point-to-point radio links

RF instrumentation

#### **GENERAL DESCRIPTION**

The ADL5350 is a high linearity, up-and-down converting mixer capable of operating over a broad input frequency range. It is well suited for demanding cellular base-station mixer designs that require high sensitivity and effective blocker immunity. Based on a GaAs pHEMT, single-ended mixer architecture, the ADL5350 provides excellent input linearity and low noise figure without the need for a high power level local oscillator (LO) drive.

In 850 MHz/900 MHz receive applications, the ADL5350 provides a typical conversion loss of only 6.8 dB. The integrated LO amplifier allows a low LO drive level, typically only 4 dBm for most applications. The input IP3 is typically greater than 25 dBm, with an input compression point of 19 dBm. The high input linearity of the ADL5350 makes the device an excellent

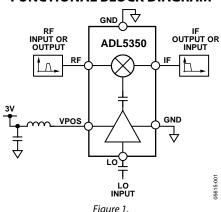

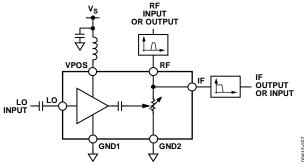

#### FUNCTIONAL BLOCK DIAGRAM

mixer for communications systems that require high blocker immunity, such as GSM 850/900 and 800 MHz CDMA2000. At 2 GHz, a slightly greater supply current is required to obtain similar performance.

The single-ended broadband RF/IF port allows the device to be customized for a desired band of operation using simple external filter networks. The LO to RF isolation is based on the LO rejection of the RF port filter network. Greater isolation may be achieved by using higher order filter networks, as described in the Applications Information section of this data sheet.

The ADL5350 is fabricated on a GaAs pHEMT, high performance IC process. The ADL5350 is available in a 3 mm x 2 mm 8-lead LFCSP. It operates over a  $-40^{\circ}$ C to  $+85^{\circ}$ C temperature range. An evaluation board is also available.

# **ADL5350**

# **Preliminary Technical Data**

# **TABLE OF CONTENTS**

| Features                                    | 1 |

|---------------------------------------------|---|

| Applications                                | 1 |

| Functional Block Diagram                    | 1 |

| General Description                         | 1 |

| Specifications                              | 3 |

| 850 MHz Receive Performance                 | 3 |

| 1950 MHz Receive Performance                | 3 |

| Spur Tables                                 | 4 |

| 850 MHz Spur Table                          | 4 |

| 1950 MHz Spur Table                         | 4 |

| Absolute Maximum Ratings                    | 5 |

| ESD Caution                                 | 5 |

| Pin Configuration and Function Descriptions | 6 |

|                                             |   |

| Typical Performance Characteristics |    |

|-------------------------------------|----|

| 850 MHz Characteristics             |    |

| 1950 MHz Characteristics            |    |

| Functional Description              | 17 |

| Circuit Description                 | 17 |

| Implementation Procedure            | 17 |

| Applications Information            | 19 |

| Low Frequency Applications          | 19 |

| High Frequency Applications         | 19 |

| Evaluation Board                    | 21 |

| Outline Dimensions                  | 22 |

| Oudaring Crida                      | 22 |

# **SPECIFICATIONS**

### **850 MHz RECEIVE PERFORMANCE**

$V_S$  = 3 V,  $T_A$  = 25°C, LO power = 4 dBm, re: 50  $\Omega$ , unless otherwise noted.

Table 1.

| Parameter                   | Min | Тур  | Max | Unit | Conditions                                                                                  |

|-----------------------------|-----|------|-----|------|---------------------------------------------------------------------------------------------|

| RF Frequency Range          | 750 | 850  | 975 | MHz  |                                                                                             |

| LO Frequency Range          | 500 | 780  | 945 | MHz  | Low-side LO                                                                                 |

| IF Frequency Range          | 30  | 70   | 250 | MHz  |                                                                                             |

| Conversion Loss             |     | 6.7  |     | dB   | $f_{RF} = 850 \text{ MHz}, f_{LO} = 780 \text{ MHz}, f_{IF} = 70 \text{ MHz}$               |

| SSB Noise Figure            |     | 6.4  |     | dB   | $f_{RF} = 850 \text{ MHz}, f_{LO} = 780 \text{ MHz}, f_{IF} = 70 \text{ MHz}$               |

| Input Third-Order Intercept |     | 25   |     | dBm  | $f_{RF1}=849$ MHz, $f_{RF2}=850$ MHz, $f_{LO}=780$ MHz, $f_{IF}=70$ MHz; each RF tone 0 dBm |

| Input 1dB Compression Point |     | 19.8 |     | dBm  | $f_{RF} = 820 \text{ MHz}, f_{LO} = 750 \text{ MHz}, f_{IF} = 70 \text{ MHz}$               |

| LO to IF Leakage            |     | 29   |     | dBc  | LO power = 4 dBm, $f_{RF}$ = 850 MHz, $f_{LO}$ = 780 MHz                                    |

| LO to RF Leakage            |     | 13   |     | dBc  | LO power = 4 dBm, $f_{RF}$ = 850 MHz, $f_{LO}$ = 780 MHz                                    |

| RF to IF Leakage            |     | 19.5 |     | dBc  | RF power = 0 dBm, $f_{RF}$ = 850 MHz, $f_{LO}$ = 780 MHz                                    |

| IF/2 Spurious               |     | -50  |     | dBc  | RF power = 0 dBm, $f_{RF}$ = 850 MHz, $f_{LO}$ = 780 MHz                                    |

| Supply Voltage              | 2.7 | 3    | 3.5 | V    |                                                                                             |

| Supply Current              |     | 16.5 |     | mA   | LO power = 4 dBm                                                                            |

### 1950 MHz RECEIVE PERFORMANCE

$V_S$  = 3 V,  $T_A$  = 25°C, LO power = 6 dBm, re: 50  $\Omega$ , unless otherwise noted.

Table 2.

| Parameter                   | Min  | Тур  | Max  | Unit | Conditions                                                                                              |

|-----------------------------|------|------|------|------|---------------------------------------------------------------------------------------------------------|

| RF Frequency Range          | 1800 | 1950 | 2050 | MHz  |                                                                                                         |

| LO Frequency Range          | 1420 | 1760 | 2000 | MHz  | Low-side LO                                                                                             |

| IF Frequency Range          | 50   | 190  | 380  | MHz  |                                                                                                         |

| Conversion Loss             |      | 6.8  |      | dB   | $f_{RF} = 1950 \text{ MHz}, f_{LO} = 1760 \text{ MHz}, f_{IF} = 190 \text{ MHz}$                        |

| SSB Noise Figure            |      | 6.5  |      | dB   | $f_{RF} = 1950 \text{ MHz}, f_{LO} = 1760 \text{ MHz}, f_{IF} = 190 \text{ MHz}$                        |

| Input Third-Order Intercept |      | 25   |      | dBm  | $f_{RF1} = 1949$ MHz, $f_{RF2} = 1951$ MHz, $f_{LO} = 1760$ MHz, $f_{IF} = 190$ MHz; each RF tone 0 dBm |

| Input 1dB Compression Point |      | 19   |      | dBm  | $f_{RF} = 1950 \text{ MHz}, f_{LO} = 1760 \text{ MHz}, f_{IF} = 190 \text{ MHz}$                        |

| LO to IF Leakage            |      | 13.5 |      | dBc  | LO power = 6 dBm, $f_{RF}$ = 1950 MHz, $f_{LO}$ = 1760 MHz                                              |

| LO to RF Leakage            |      | 10.5 |      | dBc  | LO power = 6 dBm, $f_{RF}$ = 1950 MHz, $f_{LO}$ = 1760 MHz                                              |

| RF to IF Leakage            |      | 11.5 |      | dBc  | RF power = 0 dBm, $f_{RF}$ = 1950 MHz, $f_{LO}$ = 1760 MHz                                              |

| IF/2 Spurious               |      | -54  |      | dBc  | RF power = 0 dBm, $f_{RF}$ = 1950 MHz, $f_{LO}$ = 1760 MHz                                              |

| Supply Voltage              | 2.7  | 3    | 3.5  | V    |                                                                                                         |

| Supply Current              |      | 19   |      | mA   | LO power = 6 dBm                                                                                        |

## ADL5350

## **SPUR TABLES**

All spur tables are  $N \times f_{RF} - M \times f_{LO}$ -mixer spurious products for 0 dBm input power, unless otherwise noted. N.M. indicates that a frequency was not measured. N.M. spurs are either less than -100 dBm or correspond to a frequency greater than 5995 MHz.

#### **850 MHz SPUR TABLE**

Table 3.

|   |    | M     |       |       |       |       |       |       |       |       |       |       |      |       |      |      |      |

|---|----|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|------|-------|------|------|------|

|   |    | 0     | 1     | 2     | 3     | 4     | 5     | 6     | 7     | 8     | 9     | 10    | 11   | 12    | 13   | 14   | 15   |

|   | 0  | N.M.  | -22.8 | -23.5 | -18.7 | -21.1 | -40.5 | -38.5 | -27.8 | N.M.  | N.M.  | N.M.  | N.M. | N.M.  | N.M. | N.M. | N.M. |

|   | 1  | -28.3 | -6.3  | -23.8 | -19.6 | -35.5 | -24.4 | -49.0 | -38.3 | -40.8 | N.M.  | N.M.  | N.M. | N.M.  | N.M. | N.M. | N.M. |

|   | 2  | -46.3 | -66.6 | -46.8 | -59.9 | -50.3 | -58.9 | -51.1 | -73.2 | -61.2 | -67.1 | N.M.  | N.M. | N.M.  | N.M. | N.M. | N.M. |

|   | 3  | -73.8 | -69.5 | -79.2 | -68.8 | -84.7 | -69.9 | -72.8 | -70.4 | -88.6 | -83.0 | -81.6 | N.M. | N.M.  | N.M. | N.M. | N.M. |

|   | 4  | N.M.  | -98.9 | -96.7 | N.M.  | -93.4 | N.M.  | -92.7 | -93.6 | -91.0 | N.M.  | N.M.  | N.M. | -91.5 | N.M. | N.M. | N.M. |

|   | 5  | N.M.  | N.M. | N.M.  | N.M. | N.M. | N.M. |

|   | 6  | N.M.  | N.M. | N.M.  | N.M. | N.M. | N.M. |

| N | 7  | N.M.  | N.M. | N.M.  | N.M. | N.M. | N.M. |

|   | 8  | N.M.  | N.M. | N.M.  | N.M. | N.M. | N.M. |

|   | 9  | N.M.  | N.M. | N.M.  | N.M. | N.M. | N.M. |

|   | 10 | N.M.  | N.M. | N.M.  | N.M. | N.M. | N.M. |

|   | 11 | N.M.  | N.M. | N.M.  | N.M. | N.M. | N.M. |

|   | 12 | N.M.  | N.M. | N.M.  | N.M. | N.M. | N.M. |

|   | 13 | N.M.  | N.M. | N.M.  | N.M. | N.M. | N.M. |

|   | 14 | N.M.  | N.M. | N.M.  | N.M. | N.M. | N.M. |

|   | 15 | N.M.  | N.M. | N.M.  | N.M. | N.M. | N.M. |

#### 1950 MHz SPUR TABLE

Table 4.

М 0 1 2 3 4 5 6 7 8 10 11 12 13 14 15 0 N.M. -11.7-20.1-28.5 N.M. 1 -10.6 -21.3 -25.3 -7.1-38.1N.M. N.M. 2 -48.3-60.6-44.0-44.4 -49.0-66.6 N.M. 3 -77.4-71.4-86.9-68.2-66.0-68.2-79.9N.M. N.M. N.M. N.M. N.M. N.M. N.M. N.M. N.M. 4 N.M. N.M. -94.2-92.0 -85.9 -82.9 -84.6 -90.1 N.M. N.M. N.M. N.M. N.M. N.M. N.M. N.M. 5 -99.9 -95.4 N.M. N.M. N.M. N.M. -94.2 N.M. N.M. N.M. N.M. N.M. N.M. N.M. N.M. N.M. 6 N.M. 7 N.M. 8 N.M. 9 N.M. 10 N.M. 11 N.M. 12 N.M. 13 N.M. 14 N.M. 15 N.M. N.M.

## **ABSOLUTE MAXIMUM RATINGS**

Table 5.

| Parameter                      | Rating          |

|--------------------------------|-----------------|

| Supply Voltage, V <sub>S</sub> | 4.0 V           |

| RF Input Level                 | 23 dBm          |

| LO Input Level                 | 20 dBm          |

| Internal Power Dissipation     | 324 mW          |

| $\Theta_{JA}$                  | 154.3°C/W       |

| Maximum Junction Temperature   | 135℃            |

| Operating Temperature Range    | −40°C to +85°C  |

| Storage Temperature Range      | −65°C to +150°C |

Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those indicated in the operational section of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### **ESD CAUTION**

**ESD** (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

# **ADL5350**

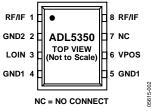

# PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

Figure 2. Pin Configuration

### **Table 6. Pin Function Descriptions**

| Pin Number | Mnemonic | Function                                                                                                                                                        |

|------------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1, 8       | RF/IF    | RF and IF Input/Output Ports. These nodes are internally tied together. RF and IF port separation is achieved using external tuning networks.                   |

| 2          | GND2     | Device Common (DC Ground) for RF/IF Switching Circuitry.                                                                                                        |

| 3          | LOIN     | LO Input, AC-Coupled.                                                                                                                                           |

| 4, 5       | GND1     | Device Common (DC Ground) for LO Buffer Circuitry.                                                                                                              |

| 6          | VPOS     | Positive Supply Voltage for the Drain of the LO Buffer. A series RF choke is needed on the supply line to provide proper ac loading of the LO buffer amplifier. |

| 7          | NC       | No Connect.                                                                                                                                                     |

## TYPICAL PERFORMANCE CHARACTERISTICS

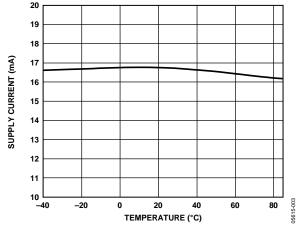

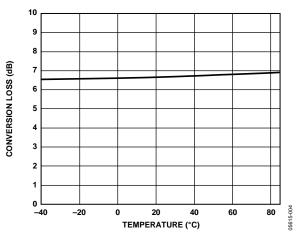

### **850 MHz CHARACTERISTICS**

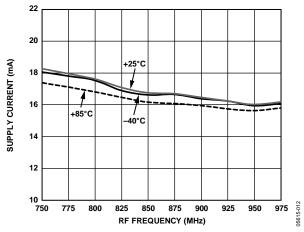

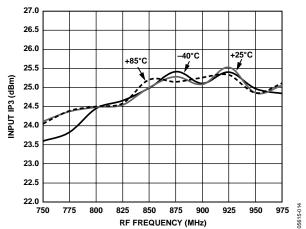

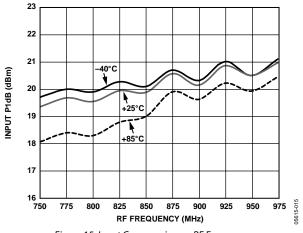

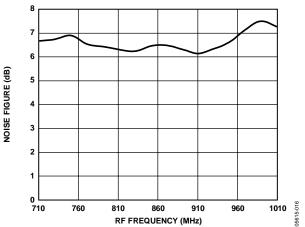

Supply voltage = 3 V, RF frequency = 850 MHz, IF frequency = 70 MHz, RF level = 0 dBm, LO level = 4 dBm, T<sub>A</sub>= 25°C, unless otherwise noted.

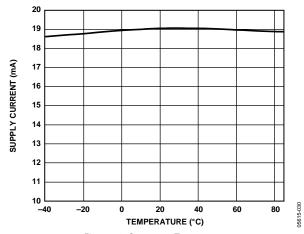

Figure 3. Current vs. Temperature

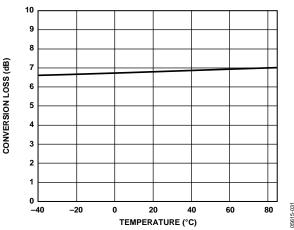

Figure 4. Conversion Loss vs. Temperature

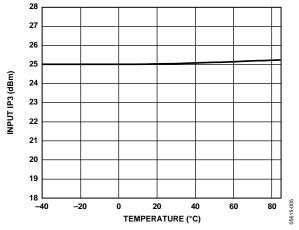

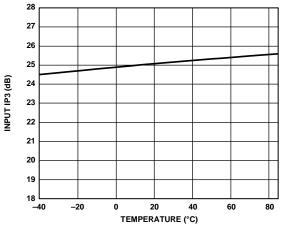

Figure 5. Input IP3(IIP3) vs. Temperature

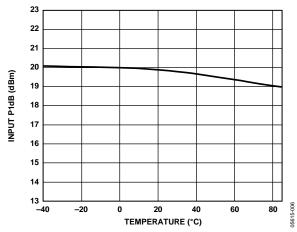

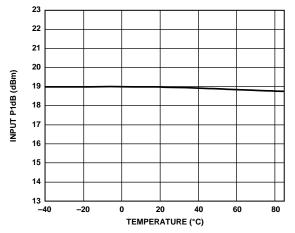

Figure 6. Input Compression vs. Temperature

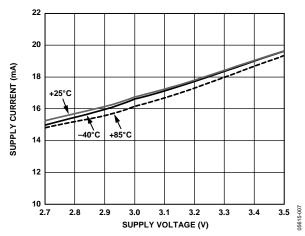

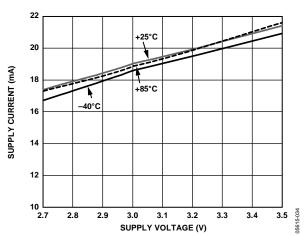

Figure 7. Current vs. Supply Voltage

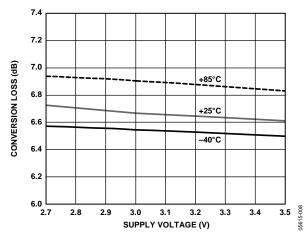

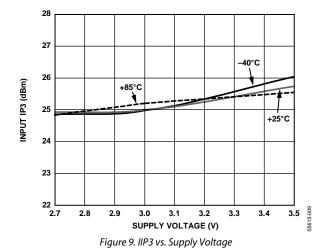

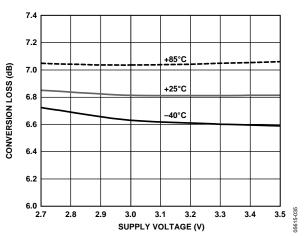

Figure 8. Conversion Loss vs. Supply Voltage

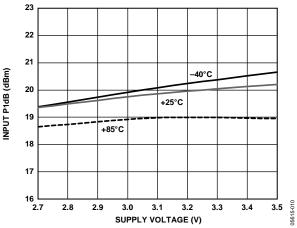

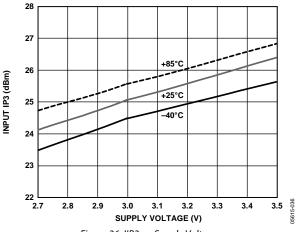

Figure 10. Input Compression vs. Supply Voltage

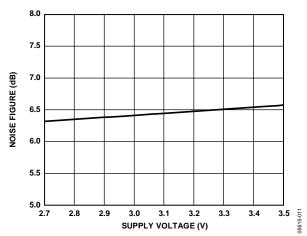

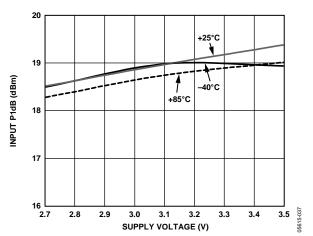

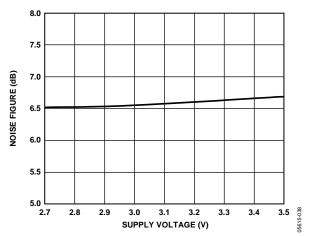

Figure 11. Noise Figure vs. Supply Voltage

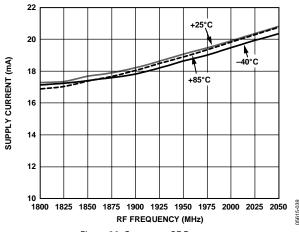

Figure 12. Current vs. RF Frequency

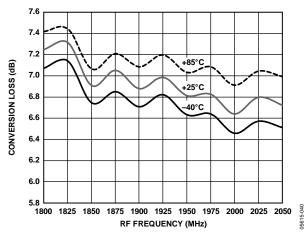

Figure 13. Conversion Loss vs. RF Frequency

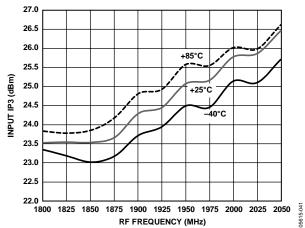

Figure 14. IIP3 vs. RF Frequency

Figure 15. Input Compression vs. RF Frequency

Figure 16. Noise Figure vs. RF Frequency

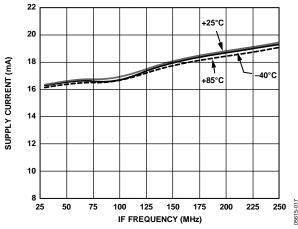

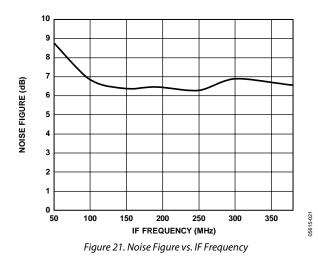

Figure 17. Current vs. IF Frequency

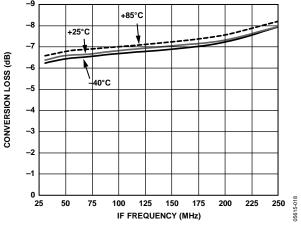

Figure 18. Conversion Loss vs. IF Frequency

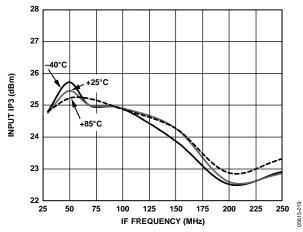

Figure 19. IIP3 vs. IF Frequency

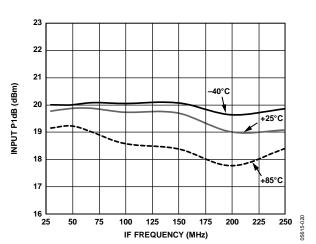

Figure 20. Input Compression vs. IF Frequency

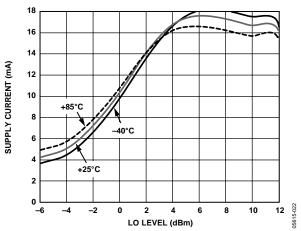

Figure 22. Current vs. LO Level

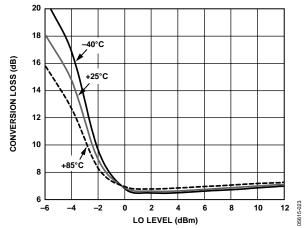

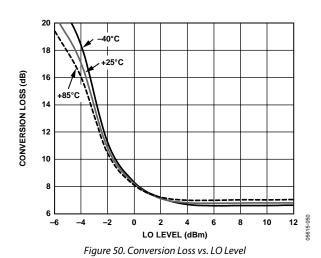

Figure 23. Conversion Loss vs. LO Level

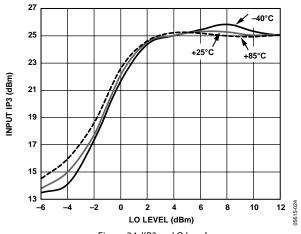

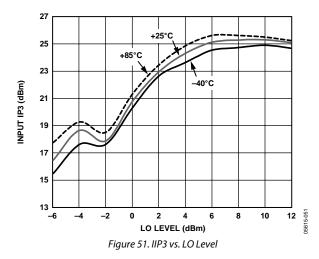

Figure 24. IIP3 vs. LO Level

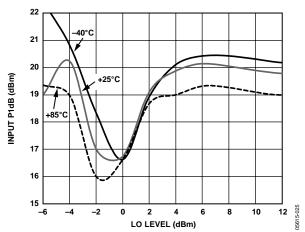

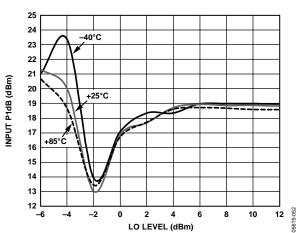

Figure 25. Input Compression vs. LO Level

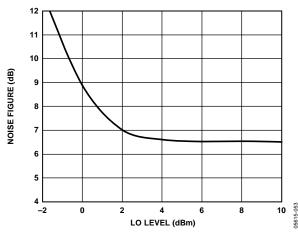

Figure 26. Noise Figure vs. LO Level

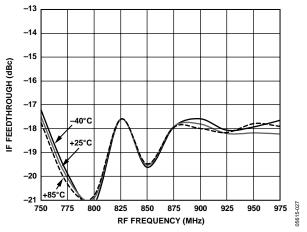

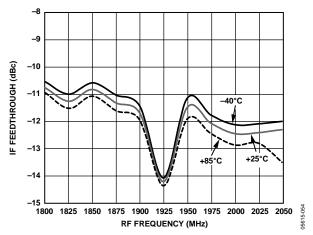

Figure 27. IF Feedthrough vs. RF Frequency

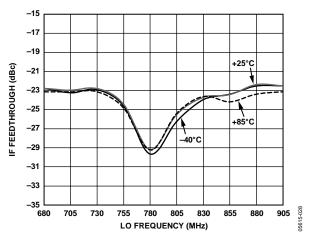

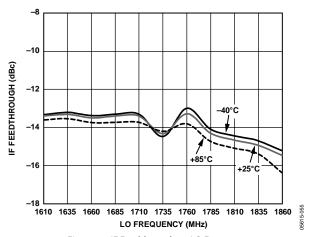

Figure 28. IF Feedthrough vs. LO Frequency

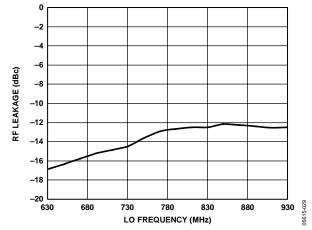

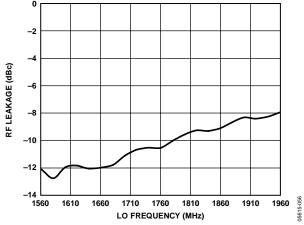

Figure 29. RF Leakage vs. LO Frequency

### 1950 MHz CHARACTERISTICS

Supply voltage = 3 V, RF frequency = 1950 MHz, IF frequency = 190 MHz, RF level = -10 dBm, LO level = 6 dBm,  $T_A = 25$ °C, unless otherwise noted.

Figure 30. Current vs. Temperature

Figure 31. Conversion Loss vs. Temperature

Figure 32. IIP3 vs. Temperature

Figure 33. Input Compression vs. Temperature

Figure 34. Current vs. Supply Voltage

Figure 35. Conversion Loss vs. Supply Voltage

Figure 36. IIP3 vs. Supply Voltage

Figure 37. Input Compression vs. Supply Voltage

Figure 38. Noise Figure vs. Supply Voltage

Figure 39. Current vs. RF Frequency

Figure 40. Conversion Loss vs. RF Frequency

Figure 41. IIP3 vs. RF Frequency

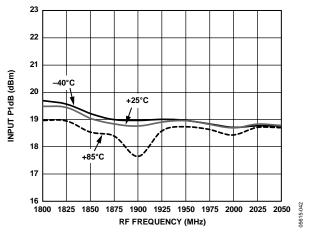

Figure 42. Input Compression vs. RF Frequency

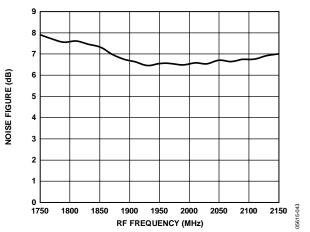

Figure 43. Noise Figure vs. RF Frequency

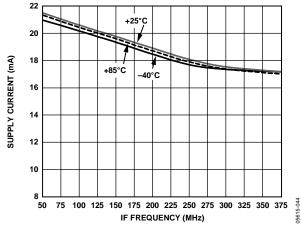

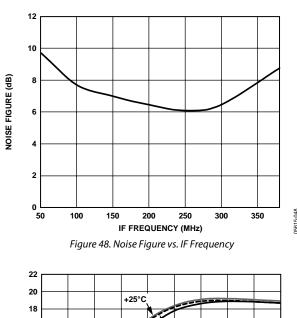

Figure 44. Current vs. IF Frequency

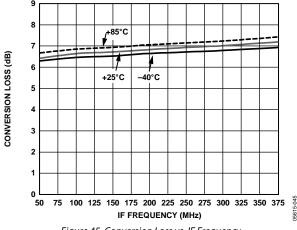

Figure 45. Conversion Loss vs. IF Frequency

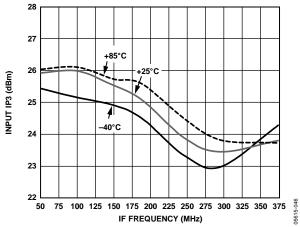

Figure 46. IIP3 vs. IF Frequency

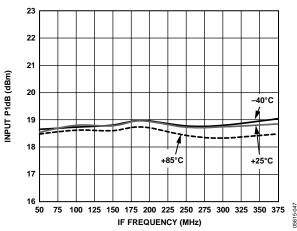

Figure 47. Input Compression vs. IF Frequency

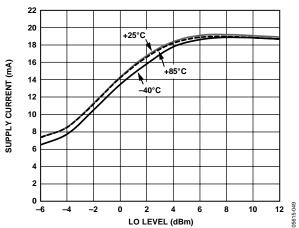

Figure 49. Current vs. LO Level

Figure 52. Input Compression vs. LO Level

Figure 54. IF Feedthrough vs. RF Frequency

Figure 55. IF Feedthrough vs. LO Frequency

Figure 56. RF Leakage vs. LO Frequency

## **FUNCTIONAL DESCRIPTION**

#### CIRCUIT DESCRIPTION

The ADL5350 is a GaAs pHEMT, single-ended, passive mixer with an integrated LO buffer amplifier. The device relies on the varying drain to source channel conductance of a FET junction to modulate an RF signal. A simplified schematic is shown in Figure 57.

Figure 57. Simplified Schematic

The LO signal is applied to the gate contact of a FET-based buffer amplifier. The buffer amplifier provides sufficient gain of the LO signal to drive the resistive switch. Additionally, feedback circuitry provides the necessary bias to the FET buffer amplifier and RF/IF ports to achieve optimum modulation efficiency for common cellular frequencies.

The mixing of RF and LO signals is achieved by switching the channel conductance from the RF/IF port to ground at the rate of the LO. The RF signal is passed through an external bandpass network to help reject image bands and reduce the broadband noise presented to the mixer. The band-limited RF signal is presented to the time-varying load of the RF/IF port, which causes the envelope of the RF signal to be amplitude modulated at the rate of the LO. A filter network applied to the IF port is necessary to reject the RF signal and pass the wanted mixing product. In a downconversion application, the IF filter network is designed to pass the difference frequency and present an open circuit to the incident RF frequency. Similarly, for an upconversion application, the filter is designed to pass the sum frequency and reject the incident RF. As a result, the frequency response of the mixer is determined by the response characteristics of the external RF/IF filter networks.

#### IMPLEMENTATION PROCEDURE

The ADL5350 is a simple single-ended mixer that relies on offchip circuitry to achieve effective RF dynamic performance. The following steps should be followed to achieve optimum performance (see Figure 58 for component designations):

Figure 58. Reference Schematic

1. Tune LO buffer supply inductor for lowest supply current.

To start this procedure, it is necessary to provide an initial guess. Table 7 can be used as a starting point. It is not necessary to terminate or populate the RF and IF port networks to complete this first step. The RF/IF pins can be left open while tuning the LO buffer networks.

Table 7. Recommended LO Bias Inductor

| Desired LO Frequency | Recommended LO Bias Inductor (L4) <sup>1</sup> |

|----------------------|------------------------------------------------|

| 380 MHz              | 68 nH                                          |

| 750 MHz              | 24 nH                                          |

| 1000 MHz             | 18 nH                                          |

| 1750 MHz             | 3.8 nH                                         |

| 2000 MHz             | 2.1 nH                                         |

<sup>&</sup>lt;sup>1</sup> The bias inductor should have a self-resonant frequency greater than the intended frequency of operation.

To test the supply current consumption, power up the device and apply the desired LO signal. Next, attempt to increase and decrease the LO frequency. If the current consumption increases as the LO frequency decreases, increase the value of L4. If the current consumption decreases as the LO frequency also decreases, decrease the value of L4. After determining the optimum inductor value, the current consumption should be minimized at the desired LO frequency.

### 2. Tune the LO port input network for optimum return loss.

Typically, a band-pass network is used to pass the LO signal to the LOIN pin. It is recommended to block high frequency harmonics of the LO from the mixer core. LO harmonics cause higher RF frequency images to be downconverted to the desired IF frequency and result in a sensitivity degradation. If the intended LO source has poor harmonic distortion and spectral purity, it may be necessary to employ a higher order band-pass filter network. Figure 58 illustrates a simple L-C band-pass filter used to pass the fundamental frequency of the LO source. Capacitor C3 is a simple DC block, while the series-inductor (L3), along with the gate-to-source capacitance of the buffer amplifier, form a low-pass network. The native gate input of the LO buffer (FET) alone presents a rather high input impedance. The gate bias is generated internally using feedback that can result in a positive return loss at the intended LO frequency.

If a better than -10 dB return loss is desired, it may be necessary to add a shunt resistor to ground before the coupling capacitor (C3) to present a lower loading impedance to the LO source.

### 3. Design the RF and IF filter networks.

Figure 58 depicts simple LC tank filter networks for the IF and RF port interfaces. The RF port LC network is designed to pass the RF input signal. The series LC tank has a resonant frequency at  $1/(2\pi\sqrt{LC})$ . At resonance, the series reactances cancel, which presents a series short to the RF signal. A parallel LC tank is used on the IF port to reject the RF and LO signals. At resonance, the parallel LC tank presents an open circuit.

It is necessary to accommodate for the board parasitics, finite Q, and self-resonant frequencies of the LC components when designing the RF, IF, and LO filter networks. Table 8 provides suggested values for initial prototyping.

Table 8. Suggested RF, IF, and LO Filter Networks for Low-Side LO Injection

|              |                        |        | · · · · · · · · · · · · · · · · · · · |        |        |        |

|--------------|------------------------|--------|---------------------------------------|--------|--------|--------|

| RF Frequency | <b>L1</b> <sup>1</sup> | C1     | L2                                    | C2     | L3     | C3     |

| 450 MHz      | 8.3 nH                 | 10 pF  | 10 nH                                 | 10 pF  | 10 nH  | 100 pF |

| 850 MHz      | 6.8 nH                 | 4.7 pF | 4.7 nH                                | 5.6 pF | 8.2 nH | 100 pF |

| 1950 MHz     | 1.7 nH                 | 1.5 pF | 1.7 nH                                | 1.2 pF | 3.5 nH | 100 pF |

| 2400 MHz     | 0.67 nH                | 1 pF   | 1.5 nH                                | 0.7 pF | 3.0 nH | 100 pF |

<sup>&</sup>lt;sup>1</sup> The inductor should have a self-resonant frequency greater than the intended frequency of operation. L1 should be a high Q inductor for optimum NF performance.

## **APPLICATIONS INFORMATION**

### LOW FREQUENCY APPLICATIONS

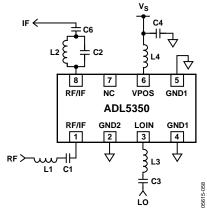

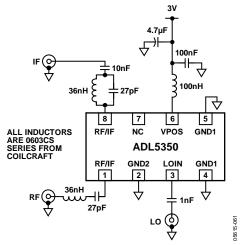

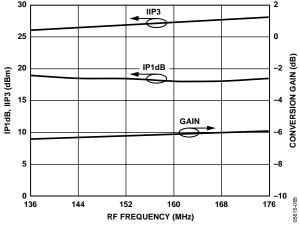

The ADL5350 can be used in low frequency applications. The circuit in Figure 59 is designed for an RF of 136 MHz to 176 MHz and an IF of 45 MHz using a high-side LO. The series and parallel resonant circuits are tuned for 154 MHz, which is the geometric mean of the wanted RF frequencies. The performance of this circuit is depicted in Figure 60.

Figure 59. RF of 136 MHz to 176 MHz Downconversion Schematic

Figure 60. Measured Performance for Circuit in Figure 59 Using High-Side LO Injection and 45 MHz IF

#### **HIGH FREQUENCY APPLICATIONS**

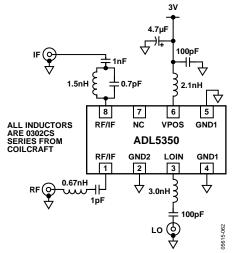

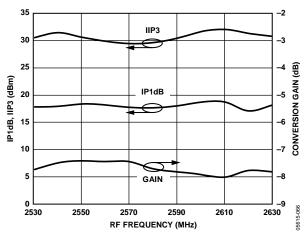

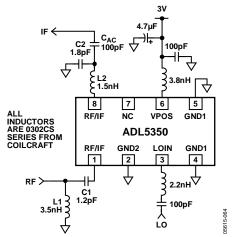

The ADL5350 can be used at extended frequencies with some careful attention to board and component parasitics. Figure 61 is an example of a 2530 MHz to 2630 MHz down-conversion using a low-side LO. The performance of this circuit is depicted in Figure 62. Note that the inductor and capacitor values are very small, especially for the RF and IF ports. Above 2.5 GHz, it is necessary to consider alternate solutions to avoid unreasonably small inductor and capacitor values.

Figure 61. 2530 MHz to 2630 MHz RF Downconversion Schematic

Figure 62. Measured Performance for Circuit in Figure 61 Using Low-Side LO Injection and 374 MHz IF

The typical networks used for cellular applications below 2.6 GHz utilize band-select and band-reject networks on the RF and IF ports. At higher RF frequencies, these networks are not easily realized by using lumped element components (discrete inductors and capacitors). As a result, it is necessary to consider alternate filter network topologies to allow more reasonable values of inductors and capacitors.

Figure 63 depicts a crossover filter network approach to provide isolation between the RF and IF ports for a downconverting application. The cross-over network essentially provides a highpass filter to allow the RF signal to pass to the RF/IF node (Pin 1 and Pin 8), while presenting a low-pass filter (which is actually a band-pass filter when considering the DC blocking capacitor,  $C_{\text{AC}}$ ). This allows the difference component ( $f_{\text{RF}}-f_{\text{LO}}$ ) to be passed to the desired IF load.

Figure 63. 3.3 GHz to 3.8 GHz RF Downconversion Schematic

When designing the RF port and IF port networks, it is important to remember that the networks share a common node (the RF/IF pins). In addition, the opposing network presents some loading impedance to the target network being designed.

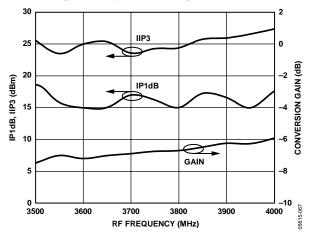

Classic audio crossover filter design techniques can be applied to help derive component values. However, some caution must be applied when selecting component values. At high RF frequencies, the board parasitics can significantly influence the final optimum inductor and capacitor component selections. Some empirical testing may be necessary to optimize the RF and IF port filter networks. The performance of the circuit depicted in Figure 63 is provided in Figure 64.

Figure 64. Measured Performance for Circuit in Figure 63 Using Low-Side LO Injection and 800 MHz IF

## **EVALUATION BOARD**

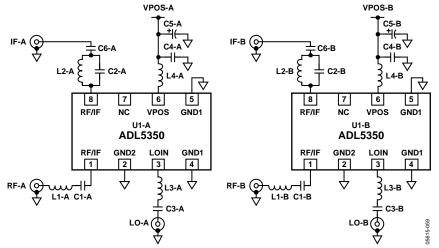

An evaluation board is available for the ADL5350. The evaluation board has two halves: a low band board designated as Board A, and a high band board designated as Board B. The schematic for the evaluation board is presented in Figure 65.

Figure 65. Evaluation Board

**Table 9. Evaluation Board Configuration Options**

| Component                             | Function                                                                                                                                                                    | Default Conditions                                                                                                                      |

|---------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|

| C4-A, C4-B, C5-A,<br>C5-B             | Supply Decoupling. C4-A and C4-B provide local bypassing of the supply. C5-A and C5-B are used to filter the ripple of a noisy supply line. These are not always necessary. | C4-A = C4-B = 100 pF,<br>C5-A = C5-B = 4.7 μF                                                                                           |

| L1-A, L1-B, C1-A,<br>C1-B             | RF Input Network. Designed to provide series resonance at the intended RF frequency.                                                                                        | L1-A = 6.8 nH (0603CS from Coilcraft),<br>L1-B = 1.7 nH (0302CS from Coilcraft),<br>C1-A = 4.7 pF, C1-B = 1.5 pF                        |

| L2-A, L2-B, C2-A,<br>C2-B, C6-A, C6-B | IF Output Network. Designed to provide parallel resonance at the geometric mean of the RF and LO frequencies.                                                               | L2-A = 4.7 nH (0603CS from Coilcraft),<br>L2-B = 1.7 nH (0302CS from Coilcraft),<br>C2-A = 5.6 pF, C2-B = 1.2 pF,<br>C6-A = C6-B = 1 nF |

| L3-A, L3-B, C3-A,<br>C3-B             | LO Input Network. Designed to block DC and optimize LO voltage swing at LOIN.                                                                                               | L3-A = 8.2 nH (0603CS from Coilcraft),<br>L3-B = 3.5 nH (0302CS from Coilcraft),<br>C3-A = C3-B = 100 pF                                |

| L4-A, L4-B                            | LO Buffer Amplifier Choke. Provides bias and ac loading impedance to LO buffer amplifier.                                                                                   | L4-A = 24 nH (0603CS from Coilcraft),<br>L4-B = 3.8 nH (0302CS from Coilcraft)                                                          |

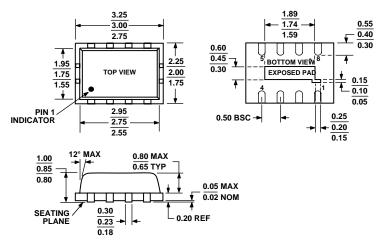

# **OUTLINE DIMENSIONS**

Figure 66. 8-Lead Lead Frame Chip Scale Package [LFCSP\_VD]

2 mm × 3 mm Body, Very Thin, Dual Lead

(CP-8-1)

Dimensions shown in millimeters

### **ORDERING GUIDE**

|                             |                   |                                                 | Package |          | Ordering        |

|-----------------------------|-------------------|-------------------------------------------------|---------|----------|-----------------|

| Model                       | Temperature Range | Package Description                             | Option  | Branding | Quantity        |

| ADL5350ACPZ-R2 <sup>1</sup> | −40°C to +85°C    | 8-Lead Lead Frame Chip Scale Package [LFCSP_VD] | CP-8-1  | Q7       | 250, Reel       |

| ADL5350ACPZ-R7 <sup>1</sup> | −40°C to +85°C    | 8-Lead Lead Frame Chip Scale Package [LFCSP_VD] | CP-8-1  | Q7       | 3000, Reel      |

| ADL5350ACPZ-WP <sup>1</sup> | −40°C to +85°C    | 8-Lead Lead Frame Chip Scale Package [LFCSP_VD] | CP-8-1  | Q7       | 50, Waffle Pack |

| ADL5350-EVALZ <sup>1</sup>  |                   | Evaluation Board                                |         |          |                 |

<sup>&</sup>lt;sup>1</sup> Z = RoHS Compliant Part.

# NOTES

| ٨ | n | L5 | . 3 | 5 | U |

|---|---|----|-----|---|---|

| M | v | Lu | U   | U | u |

**Preliminary Technical Data**

# NOTES